Paper Number(s): **E2.1**

8 6. . . . Cr. 1

**ISE2.2**

IMPERIAL COLLEGE OF SCIENCE, TECHNOLOGY AND MEDICINE UNIVERSITY OF LONDON

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING EXAMINATIONS 2001

EEE/ISE PART II: M.Eng., B.Eng. and ACGI

## **DIGITAL ELECTRONICS II**

Monday, 11 June 2:00 pm

There are FIVE questions on this paper.

Answer THREE questions.

Time allowed: 2:00 hours

Examiners:

Brookes, D.M. and Clarke, T.J.W.

Notation: Unless explicitly indicated otherwise, digital circuits throughout this paper are drawn with their inputs on the left and their outputs on the right. The notation X2:0 denotes the three-bit number X2, X1 and X0. The least significant bit of a binary number is always designated bit 0. Signals labelled with identical names are connected together. Logical negation is indicated by an exclamation mark: i.e. YX denotes the logical inversion of X.

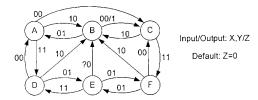

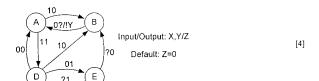

- Figure 1 shows the state diagram of a synchronous state machine having two inputs, X and Y and one output, Z. Transitions from a state to itself have been omitted. The symbol "?" denotes "don't care".

- (a) Construct the state table for the state machine including both the next state and the value of the output, Z.

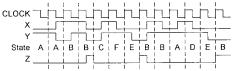

- (b) Complete the timing diagram of Figure 2 by showing the sequence of states that the state machine follows and the waveform of the output signal.

- (c) Explain what is meant by saying that two states are "equivalent".

- (d) Showing your reasoning clearly, determine which states are equivalent and hence show that it is possible to reduce the number of states to four by merging equivalent states.

- (e) Draw a state diagram for the reduced state machine.

Figure 1

Figure 2

[4]

[5]

[3]

[4]

[4]

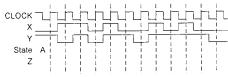

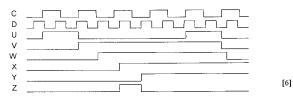

- Figure 3 shows a circuit containing four flipflops and two exclusive-or gates. The circuit

has two independent clock signals, C and D, which may have different frequencies. The

input signal, U, consists of pulses that last exactly one cycle of C and whose transitions

occur slightly after the rising edge of C.

- (a) Complete the timing diagram, showing the waveforms of V, W, X, Y and Z

- (b) If the clock signals C and D have periods c and d respectively and an arbitrary phase relationship, determine the maximum and minimum time delay between the rising edge of U and the rising edge of the corresponding output pulse at Z. You may neglect propagation delays and setup times.

- (c) Determine, as a function of c and d, the minimum interval between successive rising edges of U that will ensure that each input pulse results in a distinct output pulse at Z.

- (d) Giving your reasons fully, say which of the signals V, W, X, Y and Z are likely to contain glitches and explain the circumstances under which they may occur.

Figure 3

[6]

[5]

[5]

[4]

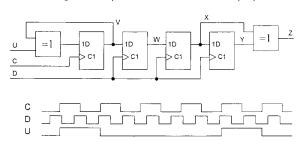

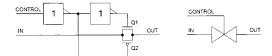

Figure 4 shows the circuit of a transmission gate consisting of two enhancement transistors and two logic gates. The figure also shows an abbreviated symbol used to represent the circuit.

The n-channel and p-channel transistor characteristics in the triode region are given by:

$$I_{D_s} = K(2V_{DS}(V_{G,S} - V_{T_s}) - V_{DS}^2)$$

and  $I_{D_s} = -K(2V_{DS}(V_{G,S} - V_{T_s}) - V_{DS}^2)$

For both transistors, the source is connected to OUT and the drain to IN. The logic gate output voltages are 0 and 5 volts and the signals IN and OUT lie in the range 0 to 5 volts.

- (a) Derive a simplified expression for the overall conductance of the transmission gate when both transistors are in the triode region of operation.

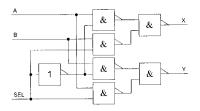

- (b) Figure 5 shows a circuit constructed from four transmission gates and an inverter. Derive Boolean expressions for the outputs, X and Y, and describe the function of the circuit.

- (c) Design a circuit using only NAND gates and inverters that performs the same function as the circuit of Figure 5.

- (d) Estimate the number of transistors required for the transmission gate implementation and for the NAND gate implementation of the circuit. You may assume that the control signal buffers within the transmission gates are shared wherever possible.

Figure 4

Figure 5

[6]

[4]

[5]

[5]

- (a) Show that adding 1 onto an unsigned binary number can be performed by inverting each bit for which all the lower significance bits are 1.

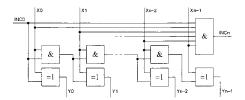

- (b) Figure 6 shows an n-bit incrementing block that adds 1 to the input number x whenever INCO is high. It contains XOR gates, 2-input AND gates and a single (n+1)-bit AND gate.

If the propagation delay of all gates is 1 unit, determine the delay to each of the changing outputs when INCO changes from 0 to 1 for each of the following circumstances:

(ii)

$$Xi = 1$$

for  $i \le (n-1)$  and  $X(n-1) = 0$

- (c) Figure 7 shows a 16-bit incrementer formed by cascading four of the incrementing blocks of Figure 6 of sizes 5, 4, 4 and 3-bits respectively. The INCn output of each stage is connected to the INC0 input of the next higher stage. Determine the worst-case delay from X0 to each of Y4, Y8, Y12 and Y15 and specify the circumstances in which each worst case arises.

- (d) Determine the maximum size of incrementer that can be formed by cascading the incrementing blocks of Figure 6 such that the worst-case delay from X0 to any Yi does not exceed 5 units. State the number of blocks required and the size of each block

Figure 6

Figure 7

[4]

[5]

[6]

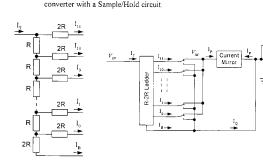

- (a) Figure 8 shows an R-2R ladder network that forms part of a 12-bit Digital-to-Analog converter. Show that, providing certain conditions are met, I<sub>k</sub> = 2<sup>k-12</sup>I<sub>T</sub>.

State the conditions needed for this to be true and give an expression for I<sub>n</sub>.

- (b) In Figure 9, the ladder is used to form a Digital-to-Analog converter. The value of R is 10kΩ and a voltage V<sub>IN</sub> of 2.048 V is applied to the input of the ladder. The current mirror reverses the direction of I<sub>P</sub>. You may assume that the voltage V<sub>M</sub> is zero.

The switches are controlled by a 12-bit unsigned binary number x which lies in the range 0 to 4095. The ladder output current  $I_z$  is sent to  $I_P$  or  $I_Q$  according to whether the  $k^{th}$  bit of x is 1 or 0 respectively. Determine expressions for  $I_P$  and  $I_Q$  and hence for  $V_{tot}$  in terms of the number x.

- (c) If the 2R resistor that carries 1<sub>r1</sub> is 0.1% too large, determine the resultant error in V<sub>out</sub> when x is equal to (i) 0, (ii) 2048, (iii) 4095.

Determine the % accuracy required of this resistor to ensure that the maximum

- error in  $V_{out}$  does not exceed ½ LSB.

(d) Explain why, in some applications, it is necessary to follow a Digital-to-Analog [4]

Figure 8

Figure 9

[4]

[6]

[6]

## 2000 E2.1/ISE2.2 Solutions

(a) From the specification in the question we get the following state table (default Z=0):

| State/Z | X,Y |    |    |    |

|---------|-----|----|----|----|

| _       | 00  | 01 | 10 | 11 |

| A       | С   | Α  | В  | D  |

| В       | C/1 | Α  | В  | В  |

| C       | С   | C  | В  | F  |

| D       | Α   | Ē  | В  | D  |

| E       | В   | F  | В  | D  |

| F       | С   | E  | В  | F  |

(b)

[5]

[4]

- (c) Two states, A and B, are equivalent if, regardless of the input signal sequence, it makes no difference to the output waveform whether the state machine's initial state is A or B [3]

- (d) (i) 0-equivalent states must have the same output under all circumstances. We therefore have two subsets: A=C=D=E=F and B. B cannot be equivalent to any other state since it has a different output when XY=01.

- (ii) 1-equivalent states must be 0-equivalent and have 0-equivalent next states. Since all states are 0-equivalent except for B, we need to check for branches to B that occur in some states but not others. The only time this happens is in state E when XY=00. Therefore our 1-equivalent subsets are: A=C=D=F, E and B.

- (iii) 2-equivalent states must be 1-equivalent and have 1-equivalent next states. We note that A and D are not 2-equivalent since they branch to A and E respectively when XY=01. For the same reason A and F are not 2-equivalent. Thus we get: A=C, D=F, E and B.

- (iv) 3-equivalent states must be 2-equivalent and have 2-equivalent next states. We get exactly the same subsets as before and these subsets are therefore equivalent.

(e) We can draw the reduced state diagram (labelling AC and DF as A and D respectively):

2. (a)

- (b) The sequence of events and their times is: U↑=0, V↑=c, W↑=c↔c+d, Z↑=c+d↔c+2d

[5]

- (c) We require the time delay between successive rising edges of Z to be at least 2d. If the time delay between successive rising edges of U is x, then we require the shortest delay from the second rising edge to be at least 2d greater than the longest delay from the first rising edge. Algebraically, this gives.

$$x+c+d>c+4d \implies x>3d$$

[5]

[4]

It is also necessary that x is a multiple of c and at least 2c.

- (d) W is likely to contain glitches if the clock frequencies are not in an exact ratio. They will occur if a rising edge of C causes V to change within the setup/hold window of the flinflop that generates W.

- Z is likely to contain glitches if W changes on successive cycles.

3. (a) The total current is given by

$$I_{D_{s}} + I_{D_{s}} = 2KV_{DS} \left( \left( V_{G_{s}S} - V_{T_{1}} - \frac{1}{2} V_{DS} \right) - \left( V_{G_{s}S} - V_{T_{2}} - \frac{1}{2} V_{DS} \right) \right)$$

Hence the conductance is

$$\frac{I_{D_1} + I_{D_2}}{V_{DN}} = 2K \left( V_{G_1 G_2} - V_{T_1} + V_{T_2} \right) = 2K \left( 5 - V_{T_1} + V_{T_2} \right)$$

[6]

(b)  $X = A \cdot |SEL + B \cdot SEL \text{ and } Y = A \cdot SEL + B \cdot |SEL$

The circuit acts as a changeover switch. If SEL = 0, it connects A to X and B to Y whereas if SEL = 1, the connections are reversed. [4]

(c)

(d) The transmission gate implementation requires 8 switch transistors and 4 transistors for the two inverters that form a non-inverting buffer. All the FET gate signals can be derived from these two inverters. Thus the total number of transistors is 12.

The NAND gate implementation requires 2 transistors for each gate input. This gives a total of 26 transistors. [5]

2000

[5]

- (a) If 1 is added onto the LSB of a number, the LSB will be inverted and a carry out will be generated from the LSB column iff the original LSB was equal to 1. This process will be repeated for successive higher order bits until we reach a bit position with a 0 in the original number. This bit will be inverted but will not generate a carry out into the next stage so all higher bits will be left unchanged.

- (b) (i) Only Y0 changes and the delay is I unit.

- (ii) All outputs change. The delay to output Yi is i+1 units. The delay to INCn is 1 unit.

[5]

- (iii) All outputs change except INCn. The delay to output Yi is i+1 units.

- (c) The delays involved in the path from Y0 to Y15 are:

Y0 to INC5 1 unit INC5 to INC 9 1 unit INC9 to INC12 1 unit INC12 to Y15 3 units

This gives a total delay of 6 units. This delay will arise iff X14:0 all equal 1.

Following a similar argument, the worst case delay from Y0 to Y4 is 5 units (iff Y3:0=1), from Y0 to Y8 is 5 units (iff Y7:0=1) and from Y0 to Y12 is 6 units (iff Y11:0=1).

(d) The maximum size of incrementer is 15 bits formed by cascading blocks of sizes 5, 4, 3, 2 and 1.

2000 Page 4 of 5 E2.1/ISE2.2 Solutions

5 (a) We assume that all the ladder outputs are held at a potential of 0 volts and use induction on the ladder order.

> Suppose that for a ladder of order n we have  $I_k = 2^{k-n}I_T$  and  $I_H = 2^{-n}I_T$ . We can form a ladder of order n+1 by re-labelling  $I_k$  as  $I_{k+1}$  and by replacing the lowest 2R resistor by a network of 3 resistors:

[4]

[6]

Both networks have an impedance of 2R to ground and the substitution will therefore not affect any of the other currents. In addition we must have  $I_o = I_B = \frac{1}{2} I_B$  since both 2R resistors have the same voltage across them. Thus we have  $I_{k+1} = I_k = 2^{(k+1)\cdot (n+1)}I_T$  and  $I_o = I_B = 1/2I_B = 2^{-(n+1)}I_T$ .

(b) The entire ladder is equivalent to a resistor R to ground and so  $I_T = V_{IN} / R = 204.8 \,\mu\text{A}$ . The current  $I_P = xI_n = 2^{-12} \, xI_T$  and  $I_O = I_T - I_P$ .

The op-amp output is given by

$$V_{OUT} = -5R(I_Q - I_P) = 5R(2I_P - I_T)$$

$$= 5RI_T (2 \times 2^{-12} \times x - 1)$$

$$= 5 \times 2^{-11}V_T (x - 2048)$$

$$= 5(x - 2048) \text{ mV}$$

[6]

(c) If the resistor carrying  $I_{11}$  is 0.1% too large, then  $I_{11}$  will be reduced by 0.1%. For x<2048, this will cause IP to decrease and IQ to increase. Thus VOUT will change by  $-2\times0.5\%\times V_{IN} = -20.48$  mV. For  $x \ge 2048$   $V_{OUT}$  will change by  $\pm 20.48$  mV. Thus the answers are (i) -20.48 mV, (ii) -20.48 mV and (iii) +20.48 mV.

To restrict changes to ½LSB = 2.5 mV, the resistor accuracy must be  $0.1\% \times 2.5/20.48 = 0.0122\%$

- (d) When several input bits change together, the switches will not switch exactly at the same time. This means that the current into the op-amp may contain a glitch which may be coupled to the output. In some applications, even a brief glitch is damaging: an example of this is the video DAC in a display. The glitch can be avoided by using a sample/hold circuit to disconnect the DAC output while it is

- [4] changing.