## **Solutions**

## 2003

# E3.06 VHDL & Logic Synthesis

Examiners: T. J. W. Clarke & P. Y. K. Cheung

#### **Solution to Question 1**

ACT, IN 7.5

This question carries 40% of total marks, and is compulsory. It examines the core material of the course as follows:

- (a) (c) test whether the student understands the use of signals, variables and control flow in synthesizable VHDL processes, and the ability to write simple hardware descriptions.

- (e) & (f) test whether the student understands the operation of VHDL testbenches. g) tests whether the student understands how to describes FSMs in VHDL

- (a) many implementations are possible here is one:

(b)

Input signals of a process occur on RHS of a concurrent assignment or in a conditional expression. In a well formed combinational process all input signals are in the sensitivity list. Output signals are those driven by the process (on LHS of concurrent assignments).

Conditions for correct synthesis:

- 1) all inputs are in sensitivity list

- 2) all outputs are driven in all execution paths through the process body.

(c) Some care is needed to ensure that all + operations are 10 bit. In theory the addition could be broken into 2 9 bit additions followed by 1 10 bit addition, thus saving 2 full adder stages. This is not required for full marks.

```

ARCHITECTURE rtl OF adder IS

BEGIN

P1: PROCESS(a,b,c,d)

VARIABLE x_v: std_logic_vector(9 DOWNTO 0);

BEGIN

pos <= '0'; -- default;

x_v := signed(a(7) & (a(7) & a)) + signed(b); -- 9 bit addition

x_v := (signed(x_v) + signed(c)) + signed(d);

x <= x_v;

IF signed(x_v) > 0 THEN

pos <= '1';

END IF;

END PROCESS P1;

END ARCHITECTURE rtl;</pre>

```

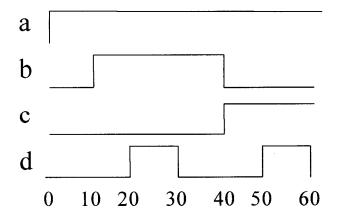

(d) Times in ns. Note no glitch on a at 30ns.

(e)

An event has non-zero delta if the event is generated from a signal assignment with zero physical delay time. Delta delays can result in flip-flop input data changing before the flip-flop is clocked, where the clock is delayed by 2 delta or more, e.g. passes through two signal assignments:

```

clk1 <= clk;

clk2 <= clk1;

FF1: PROCESS

BEGIN

WAIT UNTIL clk'EVENT AND clk='1';

q <= d;

END PROCESS FF1;

FF2: PROCESS -- this process simulates incorrectly

BEGIN

WAIT UNTIL clk2'EVENT AND clk2='1';

q2 <= d2;

END PROCESS FF2;</pre>

```

(f)

Exhaustive testing would check correct output for every possible input bit pattern. In this case there are 4 8 bit inputs => 2\*\*32 patterns. This would take a very long time to simulate. In this case a better strategy would be random testing (an independent random number for each input) for say 10000 tests together with explicit checking for all inputs at max or min values (16 cases in all).

(g)

```

ARCHITECTURE rtl OF fsm IS

TYPE state IS (s1, s2, s3);

SIGNAL ss, ss next: state;

BEGIN

P1: PROCESS(ss,x)

BEGIN

-- default values

a <= '0'; b <= '1';

ss next <= ss;

CASE ss IS

WHEN s1 =>

a <= '1';

IF x='0' THEN ss next <= s2; ELSE ss next <= s3; END IF;

WHEN s2 \Rightarrow

IF x='0' THEN ss next <= s3; ELSE ss next <= s1; END IF;

WHEN s3 =>

b <= '0';

IF x='0' THEN ss_next <= s2; END IF;</pre>

END CASE;

END PROCESS P1;

P2: PROCESS

BEGIN

WAIT UNTIL clk'EVENT AND clk='1';

IF reset = '1' THEN

ss <= s1;

ELSE

ss <= ss_next;

END IF;

END PROCESS P2;

END ARCHITECTURE rtl;

```

#### Solution to Question 2.

This question tests the student's ability to write synthesisable VHDL code. c) tests ability to design at RTL block level and d) tests ability to use structural VHDL.

```

(b)

ENTITY sorter_element IS

PORT( clk: IN std_logic;

mode: IN std_logic_vector( 1 DOWNTO 0);

in_l, in_h: IN std_logic_vector( 15 DOWNTO 0);

out_l, out_h: OUT std_logic_vector( 15 DOWNTO 0);

unchanged: OUT std_logic);

END sorter element;

```

```

ARCHITECTURE rtl OF sorter_element IS

SIGNAL data h, data l, data h d, data l d:

std logic vector(15 DOWNTO 0);

SIGNAL unchanged_int: std_logic;

BEGIN

COMB: PROCESS(data h, data 1, in h, in 1, mode)

unchanged int <= '0';</pre>

data_h_d <= data h;

data 1 d <= data 1;

CASE mode IS

WHEN "00" =>

IF sign mag_greater(data_l, data_h)

data h d <= data_l;</pre>

data 1 d <= data h;

unchanged int <= '1';

END IF;

WHEN "10" =>

data_l_d <= data_h;</pre>

data h <= in h;

WHEN "01" =>

IF sign_mag_greater( data h, in h) THEN

data h d <= in h;

unchanged int <= '1';

END IF;

IF sign_mag_greater( in_l, data_l) THEN

data 1 d <= in_1;

unchanged int <= '1';

END IF;

WHEN OTHERS => data h d <= (OTHERS =>'-');

data h 1 <= (OTHERS =>'-');

unchanged int <= '-';

END CASE;

END PROCESS COMB;

FF: PROCESS

BEGIN

WAIT UNTIL clk'EVENT AND clk='1';

data h <= data h d;

data h <= data 1 d;

END PROCESS FF;

unchanged <= unchanged int;

out h <= data h;

out 1 <= data_1;

END ARCHITECTURE rtl;

```

(c)

```

ARCHITECTURE struct OF sorter IS

TYPE array64 IS ARRAY (0 TO 64) OF std logic vector(15 DOWNTO 0);

SIGNAL z1, z2: array64;

SIGNAL x: std logic vector(63 DOWNTO 0);

CONSTANT kmax: std logic vector(15 DOWNTO 0) := (15=>'0',

OTHERS=>'1');

CONSTANT kmin: std logic vector(15 DOWNTO 0) := (OTHERS=>'1');

BEGIN

G1: FOR k IN 0 TO 63 GENERATE

I1: ENTITY WORK.sorter element PORT MAP(

clk=>clk,

mode = > m,

in h \Rightarrow z1(k),

out h \Rightarrow z2(k),

in_1 => z1(k+1),

out 1 => z2(k+1),

unchanged \Rightarrow x(k);

END GENERATE;

ANDPROC: PROCESS(x)

VARIABLE y: std_logic := '1';

BEGIN

FOR k IN 0 TO 63 LOOP

y := y AND x(k);

END LOOP;

a \ll y;

END PROCESS ANDPROC;

MUXPROC: PROCESS (m, shift in)

BEGIN

IF m = "10" THEN

z1(0) <= shift_in;

ELSE

z1(0) \le kmax;

END IF;

END PROCESS MUXPROC;

shift out \leq z1(64);

z2(64) \le kmin;

z2(0) <= shift_in;</pre>

END ARCHITECTURE struct;

```

### Solution to Question 3

Part (a) tests whether the student can understand BDDs. Part (b) tests whether the student has mastered "many-to-1" circuit description in VHDL, and part (c) tests ability to construct complex structural VHDL descriptions.

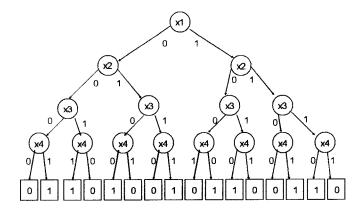

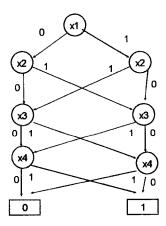

(a)

$$x1 \oplus (x2 \oplus (x3 \oplus x4))$$

#### **OBDD**

#### **ROBDD**

OBDD for n input **XOR** has  $2^n$ -1 nodes, corresponding ROBDD has 1+2(n-1) nodes. Ratio is  $2^n / (1+2(n-1)) >> 1$  (increases exponentially with n).

```

(b)

ARCHITECTURE rtl OF parity IS

BEGIN

P1: PROCESS(y)

VARIABLE zi: std logic;

BEGIN

zi := '0';

FOR j IN 0 TO n-1 LOOP

zi := zi xor y(j);

END LOOP;

z \ll zi;

END PROCESS P1;

END ARCHITECTURE rtl;

(c)

ARCHITECTURE rtl_struct OF big_parity IS

CONSTANT Unitnum: INTEGER := (M-1)/10+1;

CONSTANT ExtraInputs: INTEGER := M - UnitNum*10;

SIGNAL zi: std logic vector(UnitNum DOWNTO 0);

BEGIN

G1: FOR j IN 0 TO UnitNum-1 GENERATE

I1: ENTITY WORK.parity GENERIC MAP(10)

PORT MAP(y(j*10+9) DOWNTO j*10), zi(j));

END GENERATE;

G2: IF ExtraInputs /= 0 GENERATE

12: ENTITY WORK.parity GENERIC MAP(ExtraInputs)

PORT MAP(y( M-1 DOWNTO 10*UnitNum), zi(UnitNum));

END GENERATE;

G3: IF ExtraInputs /= 0 GENERATE

12: ENTITY WORK.parity GENERIC MAP(UnitNum+1)

PORT MAP(zi(UnitNum DOWNTO 0), z);

END GENERATE;

G4: IF ExtraInputs = 0 GENERATE

12: ENTITY WORK.parity GENERIC MAP(UnitNum+1)

PORT MAP(zi(UnitNum-1 DOWNTO 0), z);

END GENERATE;

END ARCHITECTURE rtl struct;

```

#### **Solution to Question 4**

Part (a) tests whether the student can use VHDL to write simple testbenches. Parts (b), (c) tests whether the student understands verification methodology.

```

(a)

ENTITY tb1 IS

END tb1;

ARCHITECTURE behav OF tb1 IS

TYPE ipr IS RECORD x1, x2: INTEGER; END RECORD;

TYPE ftype IS FILE OF ipr;

FILE fin: ftype OPEN read mode IS "stimulus_file";

SIGNAL clk, start i: std logic := '0';

SIGNAL done i: std logic;

SIGNAL x1_i, x2_i: std_logic_vector(14 DOWNTO 0);

SIGNAL y1 i, y2 i: std logic vector(15 DOWNTO 0);

SIGNAL y1 int, y2 int: INTEGER;

BEGIN

DUT: ENTITY WORK.testable PORT MAP( clk, start_i, done_i, x1_i,

y1_i, y2_i);

clk <= NOT clk AFTER 10 ns;

y1 int <= conv integer(unsigned(y1 i));</pre>

y2 int <= conv_integer(unsigned(y2_i));</pre>

```

```

MAIN: PROCESS

VARIABLE pair: ipr;

BEGIN

start_i <= '0';

FOR I IN 1 TO 1000 LOOP

WAIT UNTIL clk'EVENT AND clk='1';

END LOOP;

WHILE NOT endfile(fin) LOOP

read(fin, pair);

x1_i <= conv_std_logic_vector(pair.x1,15);</pre>

x2 i <= conv std logic vector(pair.x2, 15);

start i <= '1';

WAIT UNTIL clk'EVENT AND clk='1';

start i <= '0';

WAIT UNTIL clk'EVENT AND clk='1' AND done i='1';

ASSERT y1 int = fa behave(pair.x1)+fb behave(pair.x2)

REPORT "bad y1 output when x1=" & INTEGER'IMAGE(pair.x1) &

" and x2=" & INTEGER'IMAGE(pair.x2) SEVERITY error;

ASSERT y2_int = fa_behave(pair.x1)-fb_behave(pair.x2)+2**14

REPORT "bad y2 output when x1=" & INTEGER'IMAGE(pair.x1) &

" and x2=" & INTEGER'IMAGE(pair.x2) SEVERITY error;

END LOOP:

REPORT "Tests finished" SEVERITY failure;

END PROCESS MAIN;

END ARCHITECTURE behav;

```

- b) There are 2\*\*15 distinct inputs to fa, and the same number for fb. therefore 2\*\*15+2\*\*15-1=2\*\*16-1 tests are needed: fixed x1 and every x2, then fixed x2 and every value of x1, with the single duplicate test removed. This is much faster than exhaustive testing, and will check that all table values are correct with greater certainty than random testing. However it will not test that the additions to compute y1 & y2 are correct.

- c) Need to test all top 8 bit combis of x1,x2, total of 256+256=512 tests. Also need to check the interpolation. Each input is defined by:

```

(x1high, x1low, x2high, x2low)

where high = top 8 bits, low = bottom 7 bits.

Various strategies are possible, e.g. the following 1024 tests:

(x, 0, 0, 0) (x=0 to 255)

(0, 0, x, 0) (x=0 to 255)

(rnd, x, rnd, rnd) (x=0 to 255)

(rnd, rnd, rnd, x) (x=0 to 255)

```

Where each rnd is a separate randomly generated number.