**Code: AE54/AC54/AT54** Subject: LINEAR ICs & DIGITAL ELE

### **AMIETE - ET/CS/IT**

**JUNE 2013** Time: 3 Hours

Max. Marks: 10

chudentBounty.com PLEASE WRITE YOUR ROLL NO. AT THE SPACE PROVIDED ON EACH PAGE IMMEDIATELY AFTER RECEIVING THE QUESTION PAPER.

NOTE: There are 9 Questions in all.

- Question 1 is compulsory and carries 20 marks. Answer to Q. 1 must be written in the space provided for it in the answer book supplied and nowhere else.

- The answer sheet for the O.1 will be collected by the invigilator after 45 minutes of the commencement of the examination.

- Out of the remaining EIGHT Questions answer any FIVE Questions, selecting at

| Q.1 | Choose the correct or the best alternative in the following:  a. An Op-amp act as a voltage follower has a voltage gain of                                                                        |                                                                           | (2×10) |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------|

|     |                                                                                                                                                                                                   |                                                                           |        |

|     | b. A bistable multivibrator is a                                                                                                                                                                  |                                                                           |        |

|     | <ul><li>(A) Free running oscillator</li><li>(C) Saw tooth wave generator</li></ul>                                                                                                                | <ul><li>(B) Triggered oscillator</li><li>(D) Crystal oscillator</li></ul> |        |

|     | c. A virtual ground                                                                                                                                                                               |                                                                           |        |

|     | <ul> <li>(A) is a ground for voltage</li> <li>(B) is a ground for both voltage and current</li> <li>(C) is ground for current</li> <li>(D) is a ground for voltage but not for current</li> </ul> |                                                                           |        |

|     | d. An ideal differential amplifier has                                                                                                                                                            | s CMRR equaling                                                           |        |

$(\mathbf{B}) - 1$  (minus unity)

**(B)** slew rate

**(C)** Infinity (**D**) Zero

e. When a sinusoidal voltage wave is fed to a Schmitt trigger, the output will be

- (A) triangular wave (B) square wave

- (C) d.c. (D) trapezoidal wave

- f. The large signal bandwidth of an opamp is limited by its

- (C) output impedance (**D**) input frequency

- g. A 'literal' in Boolean Algebra means

- (A) a variable in its uncomplemented form only

- (B) a variable ORed with its complement

- (C) a variable in its complemented form only

- (**D**) a variable in its complemented or uncomplemented form

(A) Loop gain

(A) Unity

## StudentBour **Code: AE54/AC54/AT54** Subject: LINEAR ICs & DIGITAL ELE

- h. Simplified expression of  $xy + xyz + \overline{x}y + x\overline{y}z$  is

- (A)  $\overline{y} + x\overline{z}$

**(B)**  $\overline{x} + \overline{y}z$

(C) y + xz

- **(D)**  $y + \overline{x}z$

- i. In an SR flip flop S = 1 and R = 1 gives

- (A) Set state

- (B) Reset state

- (C) Indeterminate state

- (D) None of these

- i. The logic gate which detects equality of two bits is

- (A) EX-OR

(B) Ex-NOR

(C) NOR

(D) NAND

#### PART (A) Answer At least TWO questions. Each question carries 16 marks.

- a. Classify ICs on the basis of applications, devices used and chip complexity.(8) 0.2

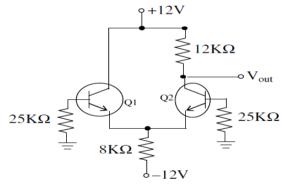

- b. In the differential amplifier circuit shown below, the transistors have identical characteristics and their  $\beta = 100$ . Determine the

- (i) output voltage

- (ii) the base currents and

- (iii) the base voltages taking into account the effect of the R<sub>B</sub> and V<sub>BE</sub>.

$R_B = 25K\Omega$ ,  $R_C = 12K\Omega$  and  $R_E = 8K\Omega$ . Assume  $V_{BE}=0.7$  Volts,

$V_{EE} = -12V$ ,  $V_{CC} = +12V$

Fig.1

- Q.3 a. Explain what you understand by 'offset voltage' and 'offset current' of op-amp. Discuss with a neat circuit diagram the technique used for minimizing offset voltage and offset current in an inverting amplifier. (10)

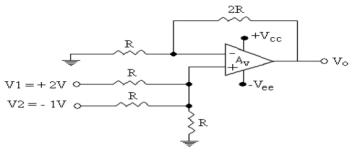

- b. Calculate the output voltage 'V<sub>0</sub>' for the following non-inverting op-amp summer with  $V_1 = 2V$  and  $V_2 = -1V$ **(6)**

# Student Bounty.com Subject: LINEAR ICs & DIGITAL ELD **Code: AE54/AC54/AT54**

Fig.2

- a. Explain Schmitt trigger with the help of transfer characteristics. Also obtain 0.4 the expression of hysteresis voltage V<sub>H</sub> and output waveform for sinusoidal input signal. **(8)**

- b. The input to an op-amp differentiator circuit is a sinusoidal voltage of peak value 10μV and frequency of 2 kHz. If the values of differentiating components are given as  $R = 40 \text{ k}\Omega$  and  $C = 3\mu\text{F}$ , determine the output voltage of differentiator circuit. **(8)**

- 0.5 a. Explain the working of R-2R Ladder Digital to Analog Converter. **(6)**

- b. Explain Monostable multivibrator circuit operation using 555 timers. Also, determine the frequency of output signal. **(6)**

- Explain the working of Series Op-Amp Regulator. **(4)**

#### PART (B) Answer At least TWO questions. Each question carries 16 marks.

- 0.6 a. Differentiate between analog and digital signals. **(4)**

- b. Explain the concept of Parity bits with reference to error detection. **(6)**

- c. Convert the following: **(6)**

- (i)  $(5A34F)_{16}$  to binary

- (ii)  $(56)_{10}$  to Gray Code

- (iii)  $(93)_{10}$  to Excess-3 Code

- **Q.7** a. Simplify the Boolean function 'F' together with don't care conditions 'd' in sum of Products

$$F(w, x, y, z) = \sum (0.1, 2.3, 7.8, 10)$$

$$d(w, x, y, z) = \sum (5.6, 11, 15)$$

(6)

- b. State and prove De Morgan's theorem using truth table. **(6)**

- c. Show that NAND gate is a Universal gate. **(4)**

- **Q.8** a. Explain the 4-bit parallel binary adder. **(8)**

- b. Write a short note on 8: 1 Multiplexers. **(8)**

- **Q.9** a. Draw and explain the working of NAND-gate latch. **(6)**

- b. Distinguish between synchronous and asynchronous counters. Design a 3-bit UP-DOWN synchronous counter. (10)